SYED FAZL UR REHMAN

Aspiration Statement

I am passionate about becoming an electrical engineer that is able to solve real-life engineering problems and enables me to impact society in a positive way. I want to pursue a career in my field that enhances my command over power electronics and feedback control.

Core Skills

- Circuit Design & Analysis

- C++, Python, Verilog

- Softwares: MATLAB, LabVIEW, OrCAD, PSpice, Vivado, Packet Tracer, PLC, Modelsim, ISE, MS office

- Devices/boards: Spartan, Zedboard (FPGA), Arduino UNO)

- Design Thinking and Data Analysis

Academic Awards / Achievements

- HU TOPS 100% Scholarship

Experience

Leadership / Meta-curricular

- Invent for the Planet’19 - Participant

- Robotics and Programming Summer Camp, Knowledge Valley School - Lead

- SIUT, Dar-ul-Sukun and Mashal Academy - Volunteered

Internship / Volunteer Work

- Jaffer Brothers (Pvt) Ltd. - Operations

- Atlas Honda - Intern

Publications / Creative Projects

- Game Development: Design and development of an interesting game for Object Oriented Programming course using C++ language.

- Voice Recognition Software: Identifying the voice of a person or animal using digital signal processing techniques.

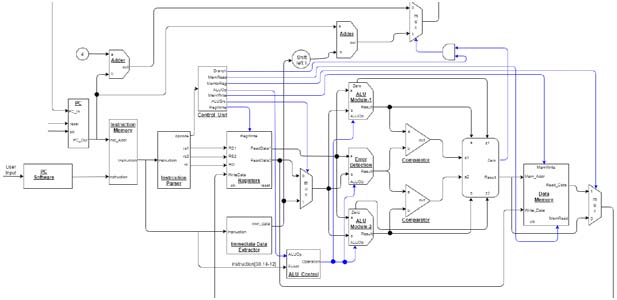

- Fault-Tolerant RISC-V Architecture: Design and Implementation of a Fault-tolerant RISC-V architecture on FPGA using Partial Reconfiguration to prevent processors in space from the effects of high radiation which may alter the functionality of the processor while performing sensitive tasks.

Final Year Project

Project Title

Design and Implementation of Fault-Tolerant RISC-V Architecture on FPGA

Description

Project Objective: Digital systems are vulnerable to run-time faults because of external conditions which alter the functionality of the circuit. There is a need of designing a fault-tolerant and self-healing the architecture along with the implementation of a soft-core processor for sensitive applications which involve highly classified data. Project Implementation Method: Implementation of the RISC-V processor is done on Zedboard (FPGA) using Vivado (software). Fault-tolerant architecture is implemented using the same software (Vivado). Communication with FPGA using software is developed in Python with the help of the Tkinter toolkit. Benefits of the Project: The sensitive defence industry requires both a fault-tolerant architecture and the FPGA integrated with open instruction set architecture (ISA). Therefore, there is a need to design a fault-tolerant RISC-V architecture and implemented it on FPGA. This novel approach will also enable educational institutes to perform quality research using the way forward. (Group Project)