ROHAN KHAN

Aspiration Statement

My career aspiration is to achieve a Masters as well as a doctorate degree in the future. Right now, I am open to career options in the field of engineering (electronic, power-systems, control-systems) as well as computer-science (machine-learning, data-science, computer architecture) or a combination of both (robotics).

Core Skills

- C++, Python

- Verilog, FPGA

- MATLAB

- Microsoft Office (Word, Excel, PowerPoint), Report Writing

- Arduino

- Artificial Intelligence (AI)

- Project Management

Academic Awards / Achievements

- Alma Mater Studiorum - Università di Bologna - Master of Science - MS Electronics Engineering: Electronics for Intelligent Systems, IoT and Big-Data (Oct 2021 - Sep 2023)

- HU TOPS 100% Scholarship

- Tensilica System Modeling Using XTSC - Certification by Cadence Design Systems

Experience

Leadership / Meta-curricular

- National Engineering Robotics Competition (NERC’18) organized by NUST - Participant

- Systems Engineering workshop and an Engineering Project Management workshop at Habib Universityt - Participant

- Norges teknisk-naturvitenskapelige universitet (NTNU) Erasmus+ Exchange Information Technology and Electronics Engineering Aug 2022 - Dec 2022

Internship / Volunteer Work

- Sahil Semiconductor Inc. - Jr. Hardware Engineer (Oct 2020 - Sep 2021)

- Pakistan Aeronaucal Complex (PAC) - Intern

- The Cizens Foundation (TCF) - Senior Volunteer

Publications / Creative Projects

- Design and implementation of a fault-tolerant RISC-V architecture: Design a fault-tolerant RISC-V architecture for need-specific applications.

- A Survey on Security Issues and Protocols in M2M Communication: The survey and investigation on security and privacy of machine to machine was done and was presented in a research paper.

Final Year Project

Project Title

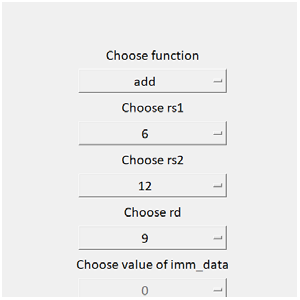

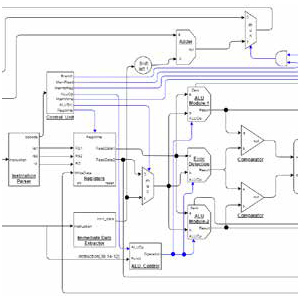

Design and Implementation of a Fault-tolerant RISC-V Architecture on FPGA

Description

Processors in space face unique challenges due to the effects of high radiation. Devices and processors used in such critical conditions require a high level of protection, accuracy and security. Keeping this scenario in mind, the aim is to design a processor with fault-tolerant capability. The approach to this problem is based on designing and implementing a RISC-V Architecture on FPGA and making it fault-tolerant. The key features of the solution include the implementation of RISC-V on FPGA which offers the advantage of reduced and simple instructions set while developing a fault-tolerant ALU for architecture is another key feature for sensitive applications. It will benefit the space exploration and aircraft manufacturing industries which demand zero tolerance levels for faults. (Group Project)